随机存取存储器

出自 MBA智库百科(https://wiki.mbalib.com/)

- 随机存取存储器(Random Access Memory,RAM)

目录 |

随机存取存储器是一种随时可以选择任一存储单元进行存入或取出数据的存储器,由于它既能读出又能写入数据,因此又称为“读/写存储器”,简称RAM。

RAM的基本结构[1]

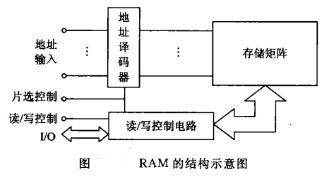

RAM一般由存储矩阵、地址译码器、片选控制和读/写控制电路等组成,如图所示。存储器有三类信号线,即数据线、地址线和控制线。

- 1)存储矩阵

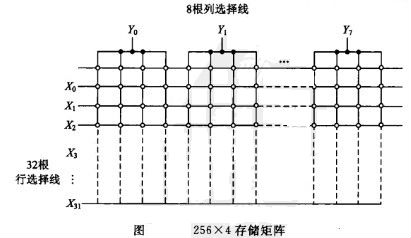

一个存储器内有许多存储单元,一般按矩阵形式排列,排成咒行和m列,存储器以字为单位组织内部结构,一个字含有若干个存储单元,一个字所含位数称为字长。实际应用中,常以字数乘字长表示存储器容量。例如,一个容量为256×4(256个字,每个字有4个存储单元)的存储器,共有1024个存储单元,可以排成32行×32列的矩阵,如图所示。图中每四列连接到一个共同的列地址译码线上,组成一个字列。每行可存储8个字,每列可存储32个字,因此需要8根列地址选择线(Y1˜Y7)、32根行地址选择线(X0˜X31)。

- 2)地址译码

通常存储器以字为单位进行数据的读写操作,每次读出或写入一个字,将存放同一个字的存储单元编成一组,并赋予一个号码,称为地址。不同的字存储单元被赋予不同的地址码,从而可以对不同的字存储单元按地址进行访问。字(存储)单元也称为地址单元。

通过地址译码器对输入地址译码,并选择相应的地址单元。在大容量存储器中,一般采用双译码结构,即有行地址和列地址,分别由行地址译码器和列地址译码器译码。行地址和列地址共同决定一个地址单元。地址单元个数N与二进制地址码的位数n有N = 2n的关系,即2n个(字)存储单元需要咒位(二进制)地址。下图中,256个字单元被赋于一个8位地址(5位行地址和3位列地址),再经各自地址译码器译成32根行地址线和8根列地址线,只有被行地址选择线和列地址选择线选中的地址单元才能对其进行数据读写操作。

- 3)输入/输出

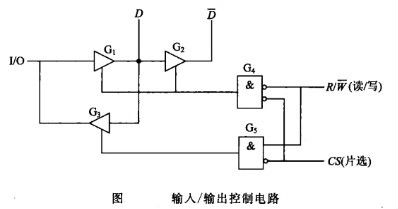

控制RAM中的输入/输出控制电路除了对存储器实现读或写操作的控制外,为了便于控制,还需要一些其他控制信号。下图给出了一个简单输入/输出控制电路,它不仅有读/写控制信号R/ ,还有片选控制信号CS。

,还有片选控制信号CS。

当片选信号CS=1时,G4,G5输出为0,三个三态缓冲器G1,G2,G3处于高阻状态,输入/输出(I/O)端与存储器内部隔离,不能对存储器进行读/写操作。当CS=0时,存储器使能;若R/ ,G5为1,G3门打开,G1,G2处于高阻状态,存储的数据D经G3输出,即实现对存储器读操作;若R/

,G5为1,G3门打开,G1,G2处于高阻状态,存储的数据D经G3输出,即实现对存储器读操作;若R/ ,G4为1,G1,G2打开,输入数据经缓冲后以互补形式出现在内部数据线上,实现对存储器写操作。

,G4为1,G1,G2打开,输入数据经缓冲后以互补形式出现在内部数据线上,实现对存储器写操作。

RAM的分类[1]

根据制造工艺的不同,随机读写存储器RAM主要有双极型和MOS型两类。双极型存储器具有存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器;MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器。

MOS型存储器按信息存放方式又可分为静态RAM(Static RAM,SRAM)和动态RAM(Dynamic RAM,DRAM)。SRAM存储电路以双稳态触发器为基础,状态稳定,只要不掉电,信息就不会丢失。其优点是不需要刷新,控制电路简单,但集成度较低,适用于不需要大存储容量的计算机系统。DRAM存储单元以电容为基础,电路简单,集成度高,但也存在问题,即电容中的电荷由于漏电会逐渐丢失,因此DRAM需要定时刷新。它适用于大存储容量的计算机系统。