隨機存取存儲器

出自 MBA智库百科(https://wiki.mbalib.com/)

- 隨機存取存儲器(Random Access Memory,RAM)

目錄 |

隨機存取存儲器是一種隨時可以選擇任一存儲單元進行存入或取出數據的存儲器,由於它既能讀出又能寫入數據,因此又稱為“讀/寫存儲器”,簡稱RAM。

RAM的基本結構[1]

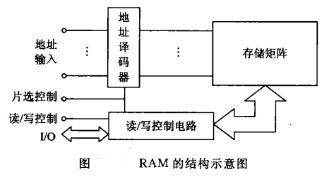

RAM一般由存儲矩陣、地址解碼器、片選控制和讀/寫控制電路等組成,如圖所示。存儲器有三類信號線,即數據線、地址線和控制線。

- 1)存儲矩陣

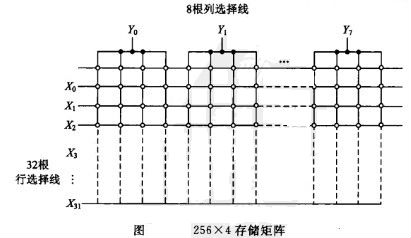

一個存儲器內有許多存儲單元,一般按矩陣形式排列,排成咒行和m列,存儲器以字為單位組織內部結構,一個字含有若幹個存儲單元,一個字所含位數稱為字長。實際應用中,常以字數乘字長表示存儲器容量。例如,一個容量為256×4(256個字,每個字有4個存儲單元)的存儲器,共有1024個存儲單元,可以排成32行×32列的矩陣,如圖所示。圖中每四列連接到一個共同的列地址解碼線上,組成一個字列。每行可存儲8個字,每列可存儲32個字,因此需要8根列地址選擇線(Y1˜Y7)、32根行地址選擇線(X0˜X31)。

- 2)地址解碼

通常存儲器以字為單位進行數據的讀寫操作,每次讀出或寫入一個字,將存放同一個字的存儲單元編成一組,並賦予一個號碼,稱為地址。不同的字存儲單元被賦予不同的地址碼,從而可以對不同的字存儲單元按地址進行訪問。字(存儲)單元也稱為地址單元。

通過地址解碼器對輸入地址解碼,並選擇相應的地址單元。在大容量存儲器中,一般採用雙解碼結構,即有行地址和列地址,分別由行地址解碼器和列地址解碼器解碼。行地址和列地址共同決定一個地址單元。地址單元個數N與二進位地址碼的位數n有N = 2n的關係,即2n個(字)存儲單元需要咒位(二進位)地址。下圖中,256個字單元被賦於一個8位地址(5位行地址和3位列地址),再經各自地址解碼器譯成32根行地址線和8根列地址線,只有被行地址選擇線和列地址選擇線選中的地址單元才能對其進行數據讀寫操作。

- 3)輸入/輸出

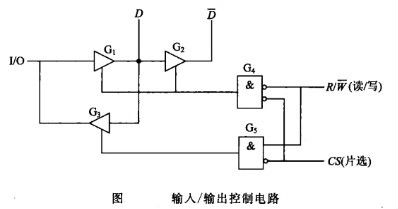

控制RAM中的輸入/輸出控制電路除了對存儲器實現讀或寫操作的控制外,為了便於控制,還需要一些其他控制信號。下圖給出了一個簡單輸入/輸出控制電路,它不僅有讀/寫控制信號R/ ,還有片選控制信號CS。

,還有片選控制信號CS。

當片選信號CS=1時,G4,G5輸出為0,三個三態緩衝器G1,G2,G3處於高阻狀態,輸入/輸出(I/O)端與存儲器內部隔離,不能對存儲器進行讀/寫操作。當CS=0時,存儲器使能;若R/ ,G5為1,G3門打開,G1,G2處於高阻狀態,存儲的數據D經G3輸出,即實現對存儲器讀操作;若R/

,G5為1,G3門打開,G1,G2處於高阻狀態,存儲的數據D經G3輸出,即實現對存儲器讀操作;若R/ ,G4為1,G1,G2打開,輸入數據經緩衝後以互補形式出現在內部數據線上,實現對存儲器寫操作。

,G4為1,G1,G2打開,輸入數據經緩衝後以互補形式出現在內部數據線上,實現對存儲器寫操作。

RAM的分類[1]

根據製造工藝的不同,隨機讀寫存儲器RAM主要有雙極型和MOS型兩類。雙極型存儲器具有存取速度快、集成度較低、功耗較大、成本較高等特點,適用於對速度要求較高的高速緩衝存儲器;MOS型存儲器具有集成度高、功耗低、價格便宜等特點,適用於記憶體儲器。

MOS型存儲器按信息存放方式又可分為靜態RAM(Static RAM,SRAM)和動態RAM(Dynamic RAM,DRAM)。SRAM存儲電路以雙穩態觸發器為基礎,狀態穩定,只要不掉電,信息就不會丟失。其優點是不需要刷新,控制電路簡單,但集成度較低,適用於不需要大存儲容量的電腦系統。DRAM存儲單元以電容為基礎,電路簡單,集成度高,但也存在問題,即電容中的電荷由於漏電會逐漸丟失,因此DRAM需要定時刷新。它適用於大存儲容量的電腦系統。