码元同步

出自 MBA智库百科(https://wiki.mbalib.com/)

目录 |

在模拟通信中,没有码元同步的问题,只有载波同步的问题,但在数字通信中,一般都有码元同步的问题。

对码元同步信号的要求有两点:一是使接收端的码元同步脉冲频率和发送端的码元速率相同;二是使接收端在最佳接收时刻对接收码元进行抽样判决,一般接收时可在码元的中间位置抽样判决,而在最佳接收时在码元的终止时刻进行抽样判决。

码元同步的目的是得知每个接收码元准确的起止时刻,以便决定积分和判决时刻。

从接收信号中获取同步信息,由其产生一时钟脉冲序列,使后者和接收码元起止时刻保持正确关系。或插入辅助同步信息。

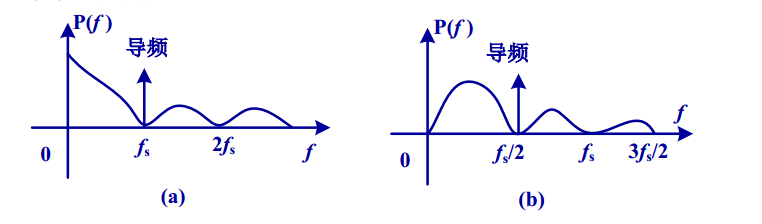

在无线通信中,数字基带信号一般都采用不归零的矩形脉冲,并以此对高频载波作各种调制。解调后得到的也是不归零的矩形脉冲,码元速率为Rs(数值上等于fs),码元宽度为Ts。这种信号的功率谱在fs处为零,例如双极性码的功率谱密度如下图(a)所示,此时可以在fs处插入位定时导频。

如果将基带信号进行相关编码,经相关编码后的功率谱密度如图(b)所示,此时可以在fs / 2处插入位定时导频,接收端取出 fs / 2以后,经过二倍频得到fs。

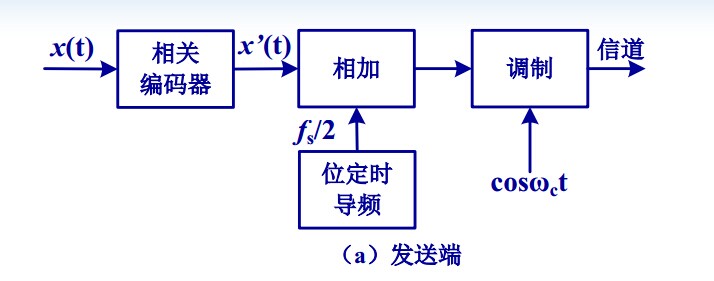

发送端插入位定时导频的框图如下:

在发送端要注意插入导频的相位,使导频相位对于数字信号在时间上有如下关系:当信号为正、负最大值(即抽样判决时刻)时,导频正好为零点,这样避免了导频对信号取样判决的影响。但即使在发端做了这样的安排,接收端仍要考虑抑制导频的问题,这是因为对信道的均衡不一定完善,即所有频率的时延不一定相等,因而信号和导频在发送端具有的时间关系会受到破坏。

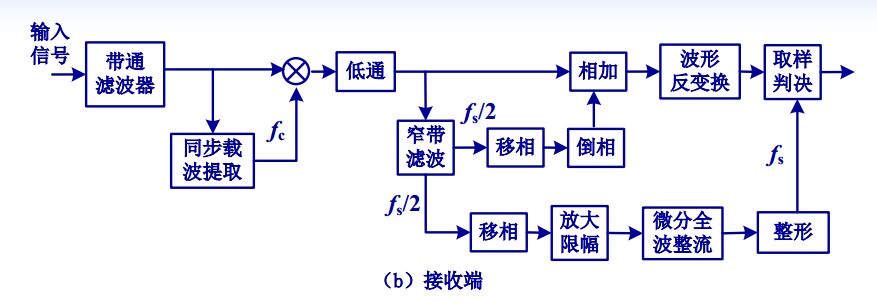

接收端提取定时导频的方框图如下:

窄带滤波器取出的导频fs / 2经过移相和倒相后,再经过相加器把基带数字信号中的导频成分抵消。由窄带滤波器取出的导频fs / 2的另一路经过移相和放大限幅、微分全波整流、整形等电路,产生位定时脉冲,微分全波整流电路起到倍频器的作用。因此,虽然导频是fs / 2,但定时脉冲的重复频率变为与码元速率相同的fs,图中两个移相器都是用来消除窄带滤波器等引起的相移,这两个移相器可以合用。

外同步法还有包络调制法及时域插入码元同步法。

所谓包络同步法,是使数字信号的包络按码元同步信号的某种波形变化。如:对已调信号进行附加的幅度调制,接收端只要进行包络检波,就可形成码元同步信号。例如BPSK信号cos[ωct + φ(t)],若用cos2πfst对它进行附加调幅后,得到已调信号为(1 + cos2πfst) * cos[ωct + φ(t)],接收端对它进行包络检波,得到包络(1 + cos2πfst),滤除直流,得到fs成分。

所谓时域插入码元同步的方法,是在传送数字信号之前先传送码元同步信息,同步信息不同于数字信息,在接收端首先鉴别出码元同步信息,再形成码元同步基准。

自同步法的接收端码元同步提取电路,从功能上讲,一般都由两部分组成:第一部分是非线性变换处理电路,它的作用是使接收信号或解调后的数字基带信号经过非线性变换处理后含有码元同步频率分量或码元同步信息。第二部分是窄带滤波器或锁相环电路,它的作用是滤除噪声和其他谱分量,提取纯净的码元同步信息。

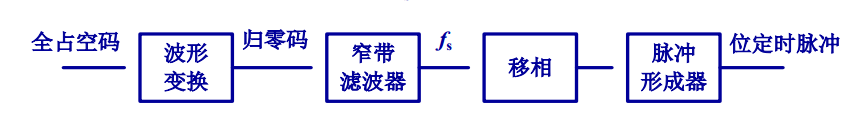

用滤波法提取。全占空的基带随机脉冲序列,不论是单极性还是双极性,当0、1等概时,都没有fs、2fs等线谱,因此不能直接滤波取出fs成分,但归零的单极性随机脉冲序列中含有fs成分,因此先对信号做变换,然后用窄带滤波器取出fs,框图如下:

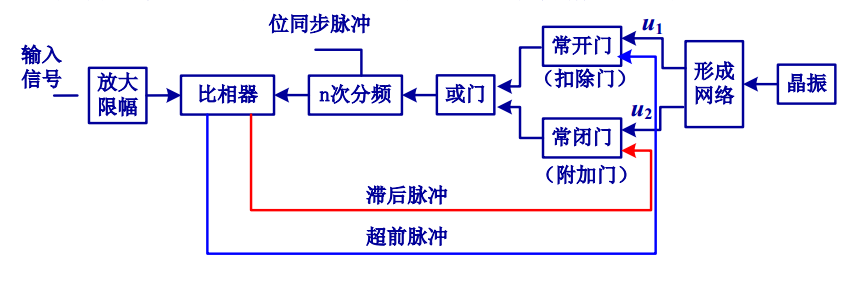

用数字锁相环来提取码元同步信息。锁相法的基本原理是在接收端利用一个相位比较器,比较接收码元与本地码元定时(位定时)脉冲的相位,若两者相位不一致,即超前或滞后,就会产生一个误差信号,通过控制电路去调整定时脉冲的相位,直至获得精确的同步为止。

由上图可知,高稳晶振产生的信号,经形成网络获得周期为T0和周期为T0但相位滞后T0 / 2的两个脉冲序列u1和u2。u1通过常开门和或门加到分频器,形成本地码元同步脉冲序列。为了与发送端时钟同步,分频器输出和接收到的码元序列进行相位比较,如果两者完全同步,此时比相器没有误差信号,本地码元同步信号作为同步时钟。

如果本地码元同步信号相位超前码元序列,比相器就输出一个超前脉冲去关闭常开门,扣除u1中的一个脉冲,使分频器输出的码元同步脉冲滞后1/n周期;如果本地码元同步脉冲比码元脉冲相位滞后时,比相器输出一个滞后脉冲去打开常闭门,使u2中的一个脉冲能通过此门和或门,

由于u1和u2相差半个周期,所以由u2中的一个脉冲插入到u1中不产生重叠,正是由于在分频前插入一个脉冲,因此,其输出同步脉冲提前1/n周期,从而实现相位的调整,若干次后,就可使本地时钟与接收码元的同步。

相位误差θe:(以锁相环法为例)同步建立并稳定后,由于收发端频率不稳及噪声影响,相位比较器在比较误差以后立即加以调整,在一个码元周期(Ts)内(相当于360相位内)加一个或扣除一个脉冲,而在一个Ts内由晶振及整形电路来的脉冲数为n个(n是分频器的分频次数),因此最大时间误差为±Ts / n,相当于最大误差为2π / n,n越大,误差越小。

同步建立时间Ts:开机工作最不利的情况是n次分频器来的码元同步脉冲与接收码元过零点脉冲相差Ts / 2,相当于晶振及整形电路输出相差n/2个脉冲,但接收码元产生的过零点脉冲不是每码元出现一个,当有连0连1时就没有,因此如果认为连0连1码的概率与0、1交替码出现的概率相等,相当于两周期(2Ts)才能调整一个脉冲,则最大的同步建立时间为0.5n * 2Ts = nTs。为了减小该值,则n就要小,与相位误差的要求矛盾。

同步保持时间tc:越长越好。

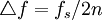

同步带宽 :指码元同步频率与码元速率之差。如果这个频差超过一定的范围,就无法使码元同步信号与输入信号同步,因此,同步带宽越小越好。数值上等于

:指码元同步频率与码元速率之差。如果这个频差超过一定的范围,就无法使码元同步信号与输入信号同步,因此,同步带宽越小越好。数值上等于  。

。